超微H100GPU促销

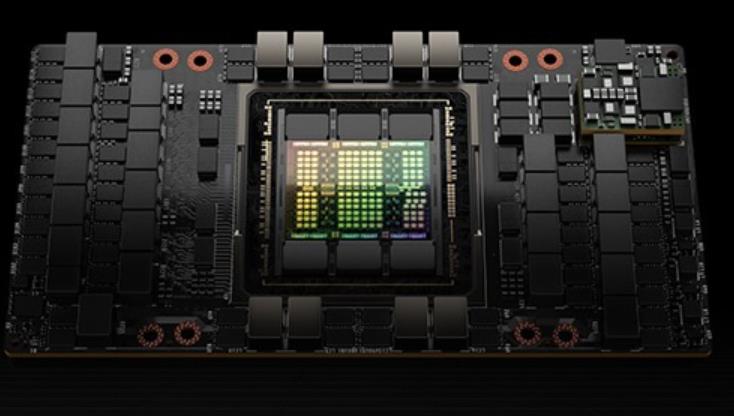

L2CacheHBM3内存控制器GH100GPU的完整实现8GPUs9TPCs/GPU(共72TPCs)2SMs/TPC(共144SMs)128FP32CUDA/SM4个第四代张量/SM6HBM3/HBM2e堆栈,12个512位内存控制器60MBL2Cache第四代NVLink和PCIeGen5H100SM架构引入FP8新的Transformer引擎新的DPX指令H100张量架构专门用于矩阵乘和累加(MMA)数学运算的高性能计算,为AI和HPC应用提供了开创性的性能。H100中新的第四代TensorCore架构提供了每SM的原始稠密和稀疏矩阵数学吞吐量的两倍支持FP8、FP16、BF16、TF32、FP64、INT8等MMA数据类型。新的TensorCores还具有更**的数据管理,节省了高达30%的操作数交付能力。FP8数据格式与FP16相比,FP8的数据存储需求减半,吞吐量提高一倍。新的TransformerEngine(在下面的章节中进行阐述)同时使用FP8和FP16两种精度,以减少内存占用和提高性能,同时对大型语言和其他模型仍然保持精度。用于加速动态规划(“DynamicProgramming”)的DPX指令新引入的DPX指令为许多DP算法的内循环提供了高等融合操作数的支持,使得动态规划算法的性能相比于AmpereGPU高提升了7倍。L1数据cache和共享内存结合将L1数据cache和共享内存功能合并到单个内存块中简化了编程。H100 GPU 优惠促销,马上下单。超微H100GPU促销

在大预言模型中达到9倍的AI训练速度和30倍的AI推理速度。HBM3内存子系统提供近2倍的带宽提升。H100SXM5GPU是世界上款采用HBM3内存的GPU,其内存带宽达到3TB/sec。50MB的L2Cache架构缓存了大量的模型和数据以进行重复访问,减少了对HBM3的重复访问次数。第二代多实例GPU(Multi-InstanceGPU,MIG)技术为每个GPU实例提供约3倍的计算能量和近2倍的内存带宽。次支持机密计算,在7个GPU实例的虚拟化环境中支持多租户、多用户配置。(MIG的技术原理:作业可同时在不同的实例上运行,每个实例都有的计算、显存和显存带宽资源,从而实现可预测的性能,同时符合服务质量(QoS)并尽可能提升GPU利用率。)新的机密计算支持保护用户数据,防御硬件和软件攻击,在虚拟化和MIG环境中更好的隔离和保护虚拟机。H100实现了世界上个国产的机密计算GPU,并以全PCIe线速扩展了CPU的可信执行环境。第四代NVIDIANVLink在全归约操作上提供了3倍的带宽提升,在7倍PCIeGen5带宽下,为多GPUIO提供了900GB/sec的总带宽。比上一代NVLink增加了50%的总带宽。第三代NVSwitch技术包括驻留在节点内部和外部的交换机,用于连接服务器、集群和数据中心环境中的多个GPU。超微H100GPU how muchH100 GPU 降价促销,机会难得。

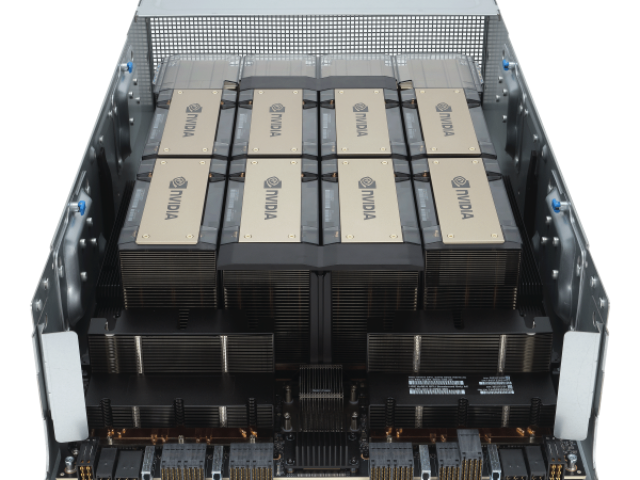

网络、存储、RAM、CPU)以及销售它的人的利润率和支持级别。该范围的**,包括支持在内的$360k-380k,是您可能期望与DGXH100相同规格的。1xHGXH100(PCIe)和8xH100GPU大约是300k美元,包括支持,具体取决于规格。PCIe卡的市场价格约为30k-32k美元。SXM卡并不是真正作为单张卡出售的,因此很难在那里给出定价。通常作为4-GPU和8-GPU服务器出售。大约70-80%的需求是SXMH100,其余的是PCIeH100。SXM部分的需求呈上升趋势,因为PCIe卡是前几个月***可用的卡。鉴于大多数公司购买8-GPUHGXH100(SXM),每360个H380的大约支出为8k-100k,包括其他服务器组件。DGXGH200(提醒一下,包含256xGH200,每个GH200包含1xH100GPU和1xGraceCPU)的成本可能在15mm-25mm之间-尽管这是一个猜测,而不是基于定价表。19需要多少个GPU?#GPT-4可能在10,000到25,000架A100之间接受过训练。20Meta拥有大约21,000架A100,特斯拉拥有约7,000架A100,稳定AI拥有约5,000架A100。21猎鹰-40B在384架A100上进行了训练。22Inflection使用3,500H100作为其。23顺便说一句,到22月,我们有3k在运行。并且***运行超过5.<>k。——穆斯塔法·苏莱曼(MustafaSuleyman)。

因此线程可以自由地执行其他**的工作。②终线程需要其他所有线程产生的数据。在这一点上,他们做一个"等待",直到每个线程都有"抵达"的信号。-***是允许提前到达的线程在等待时执行**的工作。-等待的线程会在共享内存中的屏障对象上自转(spin)(我理解的就是这些等待的线程在等待的时候无法执行其他工作)也是一个分裂的屏障,但不对到达的线程计数,同时也对事务进行计数。为写入共享内存引入一个新的命令,同时传递要写入的数据和事务计数。事务计数本质上是对字节计数异步事务屏障会在W**t命令处阻塞线程,直到所有生产者线程都执行了一个Arrive,所有事务计数之和达到期望值。异步事务屏障是异步内存拷贝或数据交换的一种强有力的新原语。集群可以进行线程块到线程块通信,进行隐含同步的数据交换,集群能力建立在异步事务屏障之上。H100HBM和L2cache内存架构HBM存储器由内存堆栈组成,位于与GPU相同的物理封装上,与传统的GDDR5/6内存相比,提供了可观的功耗和面积节省,允许更多的GPU被安装在系统中。H100 GPU 特惠销售,快来选购。

使用TSMC4nm工艺定制800亿个晶体管,814mm²芯片面积。NVIDIAGraceHopperSuperchipCPU+GPU架构NVIDIAGraceCPU:利用ARM架构的灵活性,创建了从底层设计的CPU和服务器架构,用于加速计算。H100:通过NVIDIA的超高速片间互连与Grace配对,能提供900GB/s的带宽,比PCIeGen5快了7倍目录H100GPU主要特征基于H100的系统和板卡H100张量架构FP8数据格式用于加速动态规划(“DynamicProgramming”)的DPX指令L1数据cache和共享内存结合H100GPU层次结构和异步性改进线程块集群(ThreadBlockClusters)分布式共享内存(DSMEM)异步执行H100HBM和L2cache内存架构H100HBM3和HBM2eDRAM子系统H100L2cache内存子系统RAS特征第二代安全MIGTransformer引擎第四代NVLink和NVLink网络第三代NVSwitch新的NVLink交换系统PCIeGen5安全性增强和保密计算H100video/IO特征H100GPU主要特征新的流式多处理器(StreamingMultiprocessor,SM)第四代张量:片间通信速率提高了6倍(包括单个SM加速、额外的SM数量、更高的时钟);在等效数据类型上提供了2倍的矩阵乘加。MatrixMultiply-Accumulate,MMA)计算速率,相比于之前的16位浮点运算,使用新的FP8数据类型使速率提高了4倍。H100 GPU 的基础时钟频率为 1410 MHz。戴尔H100GPU stock

H100 GPU 的单精度浮点计算能力为 19.5 TFLOPS。超微H100GPU促销

H100 GPU 在视频编辑中也展现了其的性能。它能够快速渲染和编辑高分辨率视频,提升工作效率。无论是实时预览、处理还是多层次剪辑,H100 GPU 都能流畅应对,减少卡顿和渲染时间。其高带宽内存和并行处理能力确保了视频编辑过程的流畅和高效,使视频编辑工作变得更加轻松和高效,是视频编辑领域的理想选择。H100 GPU 在云计算平台中的应用也非常。其高并行处理能力和大带宽内存使云计算平台能够高效地处理大量并发任务,提升整体服务质量。H100 GPU 的灵活性和易管理性使其能够轻松集成到各种云计算架构中,满足不同客户的需求。无论是公共云、私有云还是混合云环境,H100 GPU 都能提供强大的计算支持,推动云计算技术的发展和普及。超微H100GPU促销

上一篇: N9K-C92348GC-X 厂家

下一篇: N9K-C9300-ACK 优惠价